Product Summary

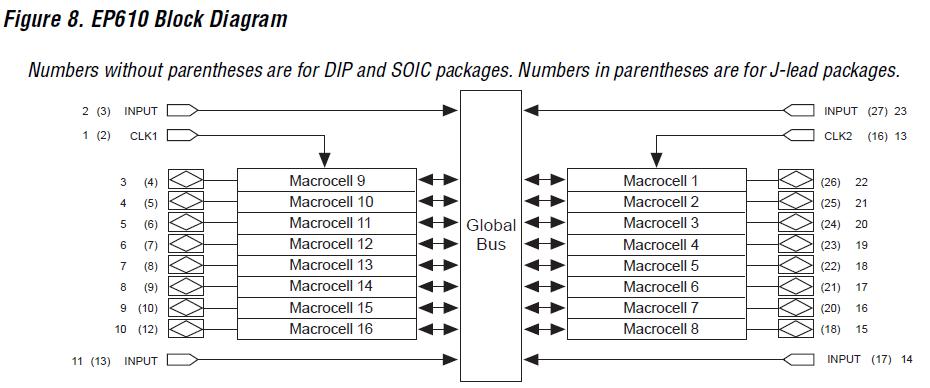

The ep610pc-25 is an EPLD. It has 16 macrocells, 4 dedicated input pins, 16 I/O pins, and 2 global clock pins (see Figure 8). Each macrocell of the ep610pc-25 can access signals from the global bus, which consists of the true and complement forms of the dedicated inputs and the true and complement forms of either the output of the macrocell or the I/O input. The CLK1 signal of the ep610pc-25 is a dedicated global clock input for the registers in macrocells 9 through 16. The CLK2 signal is a dedicated global clock input for registers in macrocells 1 through 8.

Parametrics

ep610pc-25 absolute maximum ratings: (1)Supply voltage: –2.0 to 7.0 V With respect to ground; (2)DC input voltage: –2.0 to 7.0 V; (3)DC VCC or ground current: –175 to 175 mA; (4)DC output current, per pin: –25 to 25 mA; (5)Storage temperature No bias: –65 to 150 ℃; (6)Ambient temperature Under bias: –65 to 135 ℃; (7)Junction temperature Ceramic packages, under bias: 150 ℃; Plastic packages, under bias: 135 ℃.

Features

ep610pc-25 features: (1)Complete device family with logic densities of 300 to 900 usable gates; (2)Device erasure and reprogramming with non-volatile EPROM configuration elements; (3)Fast pin-to-pin logic delays as low as 10 ns and counter frequencies as high as 100 MHz; (4)24 to 68 pins available in dual in-line package (DIP), plastic J-lead chip carrier (PLCC), pin-grid array (PGA), and small-outline integrated circuit (SOIC) packages; (5)Programmable security bit for protection of proprietary designs; (6)100% generically tested to provide 100% programming yield; (7)Programmable registers providing D, T, JK, and SR flipflops with individual clear and clock controls.

Diagrams

|

EP610I |

Other |

|

Data Sheet |

Negotiable |

|

||||

(China (Mainland))

(China (Mainland))